www.engineering-japan.com

14

'21

Written on Modified on

車載アナログIC向け高耐圧LDMOSの静電破壊耐量と電力効率を 両立させる技術を開発

東芝デバイス&ストレージ株式会社(以下、東芝デバイス&ストレージ)と株式会社ジャパンセミコンダクター(以下、ジャパンセミコンダクター)は、車載アナログIC向けの高耐圧LDMOS注1において、従来トレードオフの関係を持つと考えられていた静電破壊耐量と電力効率が両立可能であることを明らかにしました。

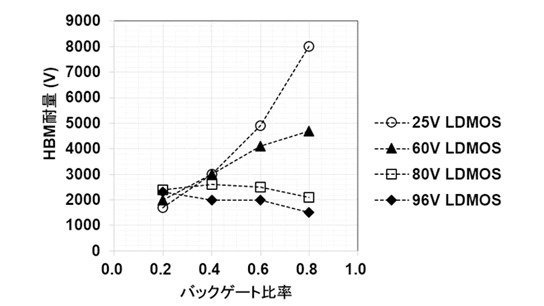

静電気破壊耐性の一つである人体帯電モデル(HBM)注2耐量とバックゲート比率注3の関係性を検証することで、耐圧に応じてデバイスに適したデザインを選択することができるようになりました。

モータ―コントロールドライバーなどのアナログICは、さまざまな自動車部品に搭載されており、電気自動車の普及や先進運転支援システム搭載車の増加などを背景に、継続的な市場拡大が見込まれています。一方、車載半導体は高い信頼性を保持することが不可欠であり、アナログICの一部を構成するLDMOSにおいても、性能改善と信頼性向上の両立が課題となっています。これまで、信頼性指標の一つであるHBM耐量は、バッグゲート比率を上げると、デバイスの横方向に作用する寄生バイポーラ動作注4が抑制されるため、向上するとされていました。ただし、バックゲート比率に比例してオン抵抗も増大してしまうため、HBM耐量の向上とオン抵抗の低減はトレードオフの関係にあると考えられてきました。

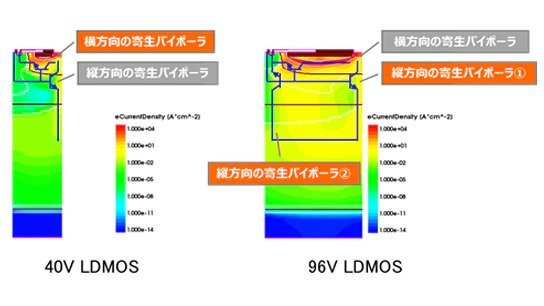

東芝デバイス&ストレージとジャパンセミコンダクターは、複数の耐圧でLDMOSのHBM耐量を評価し、デバイスの動作をシミュレーションしました。その結果、耐圧が80V以上のLDMOSでは、横方向だけでなく縦方向の寄生バイポーラが動作するため、バッグゲート比率はHBM耐量に比例しないことが判明しました。すなわち、HBM耐量を向上させるためにオン抵抗の上昇をもたらすバックゲート比率を上げる必要はなく、両指標を別々に調整できるようになります。株式会社東芝が2016年に開発した技術注5により、バッグゲート比率以外の設計指標を最適化することができるため、今回の検証結果と組み合わせることで、耐圧80V以上のLDMOSにおいて、オン抵抗の上昇を抑えながらHBM耐量の向上を実現することができます。耐圧80V以上の高耐圧LDMOSを搭載したアナログICは主に電動パワーステアリングやエンジンなどに使用可能であり、今回の技術はこれらの機器の信頼性向上と電力損失低減に貢献します。

東芝デバイス&ストレージは、今回の技術の詳細を、5月30日から6月3日までオンラインで開催された半導体の国際学会「IEEE International Symposium on Power Semiconductor Devices and ICs (ISPSD) 2021」において発表しました。

なお、東芝デバイス&ストレージは、今回開発したLDMOS以外にも、耐圧や用途に応じてさまざまなLDMOSをラインアップしており、現在は第五世代プロセスの開発を進めています。第五世代プロセスは、高耐圧アナログICに車載向け不揮発性メモリーを混載(eNVM)している点が特長です。

東芝デバイス&ストレージとジャパンセミコンダクターは今後も、両社の強みを生かしたプロセス技術の開発を加速し、車載向けをはじめとする幅広い領域で付加価値の高いアナログICを展開していきます。

注1 LDMOS:Laterally Double Diffused MOSの略。耐圧向上を目的として、ドレイン近傍から横方向に不純物拡散領域(ドリフト領域)を持たせたMOSFETのこと。

注2 HBM(Human Body Model):人体が静電気の発生源となり、そこから静電気放電が生じることでデバイスに損傷を起こすことを想定したモデルのこと。HBM耐量が高いと、静電気によるデバイスの損傷に対する耐性が高い。

注3 バックゲート比率:東芝デバイス&ストレージでは、LDMOSのソースとバックゲートの取り出し拡散層を縦方向に交互に配置しており、バッグゲート比率は、ソース幅とバックゲート幅の合計値に占めるバックゲート幅の割合のことを指す。

注4 寄生バイポーラ動作: HBMテスト時にLDMOSのドレインに正の電圧を印加すると、PN接合部でインパクトイオンが発生し、ドレイン/ボディ/ソースがそれぞれコレクター/ベース/エミッターとなりコレクター電流が流れる現象のこと。このコレクター電流がSi表面で電流集中して高熱が発生しSiが溶融することで素子破壊に至る。

注5 当該技術の詳細はISPSD2017において株式会社東芝(分社化による東芝デバイス&ストレージ設立前。現在、該当部門は東芝デバイス&ストレージの組織。)が発表した論文を参照。(論文タイトル: “HBM robustness optimization of fully isolated Nch-LDMOS for negative input voltage using unique index parameter.”)

HBM耐量とバックゲート比率の関係性(当社調べ)

耐圧による寄生バイポーラ動作の違いを示すESDシミュレーション結果(当社調べ)

低耐圧(40V)では横方向の寄生バイポーラ動作が支配的だが、高耐圧(96V)では縦方向にも寄生バイポーラが有効に動作する。

www.toshiba.com