高密度実装可能なP-SON4パッケージの高阻止電圧定格フォトリレーのラインアップ拡充 : TLP3483、TLP3484

当社は、2.54SOPパッケージと比べて実装面積を削減した P-SON4パッケージのフォトリレー「TLP3483、TLP3484」を製品化し、TLP348xシリーズのラインアップを拡充しました。

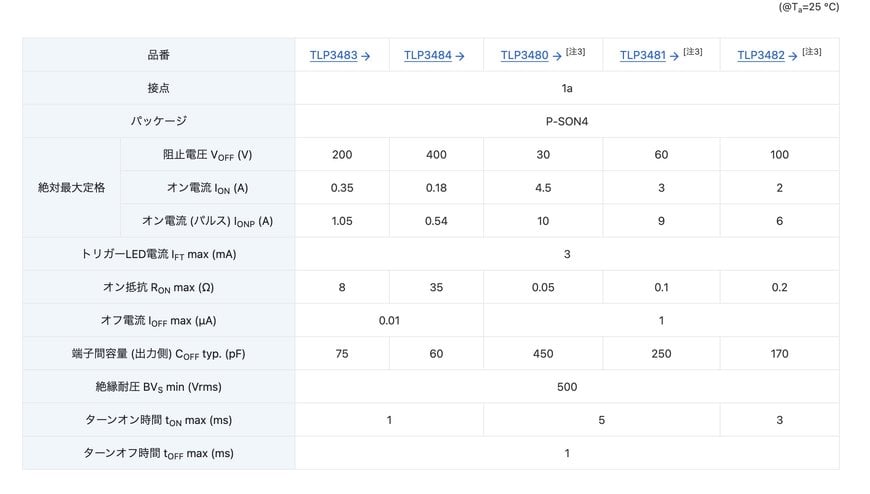

新製品は、受光側に当社新プロセス[注1]の高耐圧MOSFETチップを使用し、高い阻止電圧定格を実現しました。阻止電圧定格は、TLP3483が200 V、TLP3484が400 Vです。これにより、幅広いテスター用途で使用できます。

パッケージは、実装面積7.14 mm2 (typ.) のP-SON4を採用し、2.54SOP4と比べて約74 %、2.54SOP6と比べて約84 %小型化し、高密度実装が可能です。

ラインアップ拡充により、TLP348xシリーズは、阻止電圧定格が30 V/60 V/100 V/200 V/400 Vの5品種となります。

[注1] 二重拡散構造のπ-MOSプロセス

特長

阻止電圧定格が高い

- TLP3483 : 阻止電圧定格 200 V、オン電流定格 0.35 A

- TLP3484 : 阻止電圧定格 400 V、オン電流定格 0.18 A

小型パッケージP-SON4 : 2.1 mm x 3.4 mm (typ.)、実装面積 7.14 mm2 (typ.)

用途

- 半導体テスター (メモリー、SoC、LSI、ディスクリートなど)[注2]

- プローブカード

- I/O インターフェースボード

[注2] TLP3484は半導体テスター専用

製品仕様

[注3] 先行リリース製品

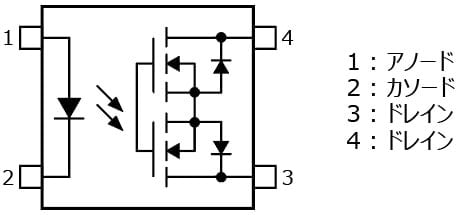

端子配置図

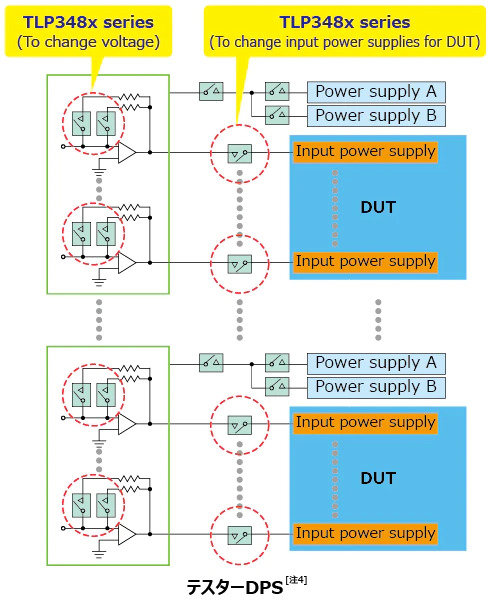

応用回路例

[注4] DPS (Device Power Supply) : 被試験デバイスに電源を供給するための計測部の一部

www.toshiba.com