組込み向け100Gbps RoCEv2 RDMA IPを開発

Intellectual Highway株式会社が、CPU非依存の超低遅延メモリ転送をFPGAで実現するRDMA IPを提供。

www.i-highway.com

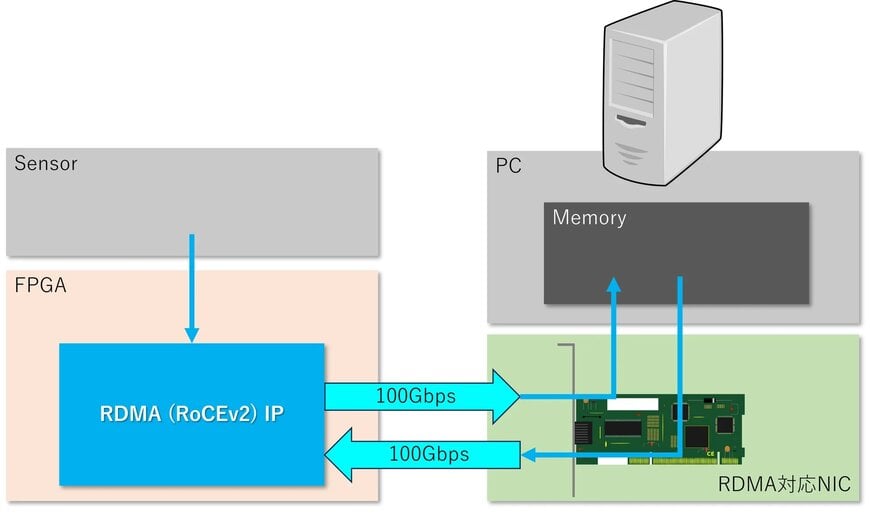

Intellectual Highway株式会社は、FPGA上で高帯域データをRDMA(RoCEv2)プロトコルに変換し、CPUリソースを使用せずにリモートメモリアクセスを可能にする組込み向けIPを開発した。本技術は、100Gbpsクラスの低遅延データ転送が求められるAI、半導体製造、映像、医療機器分野での利用を想定している。

RDMA技術が求められる背景

AI学習やHPC用途のデータセンターでは、高帯域かつ低遅延でのメモリ転送を実現する手段としてRDMA(Remote Direct Memory Access)が標準的に採用されている。RDMAは、ネットワーク通信時にCPUを介さずNICとメモリ間で直接データを転送する仕組みであり、CPU負荷の削減とレイテンシ低減を同時に実現できる。

近年、この仕組みはデータセンターに限らず、組込み分野へも応用が進んでいる。半導体製造装置における高帯域センサーデータ転送、非圧縮の高解像度映像伝送、医療画像処理装置などでは、CPU処理を伴わない安定した低遅延通信が技術要件となっている。

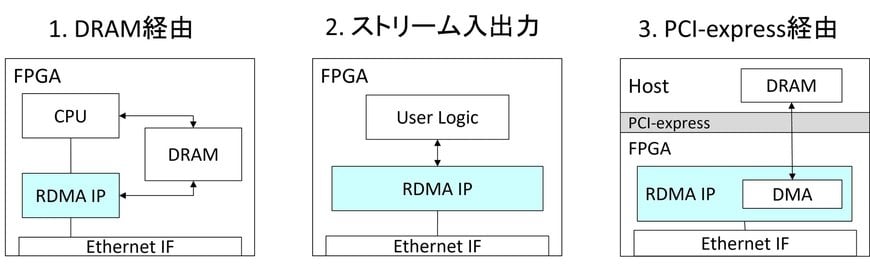

IPのデータ入出力形式

組込み用途に向けた設計思想

今回提供されるRoCEv2 RDMA IPは、FPGAに直接実装することを前提とし、従来のメモリベース転送に加えてストリーム入出力インターフェースを備える点が特長である。ストリーム方式では、データを一時的にDRAMへ格納することなく転送でき、1マイクロ秒未満のレイテンシを実現する。

また、RoCEv2で必要となるコネクション管理(Communication Management Message)をIP内部で処理する構成を採用しており、接続確立やハンドシェイクにCPUを必要としない。これにより、FPGA単体で完結したRDMA通信が可能となる。

対応インターフェースと適用例

本IPは、DRAM経由、ストリーム入出力、PCI Express経由の3種類のデータ入出力方式に対応する。センサや画像入力を直接ストリームとして扱う構成から、ホストシステムとPCIeで接続する構成まで、用途に応じた設計が可能である。

想定される利用例としては、FPGAを搭載した計測・センシング装置と、RDMA対応NICを備えたサーバ間でのリアルタイムデータ転送などが挙げられる。

技術仕様

本IPはRoCEv2を中心に、ARPおよびICMP(Ping)に対応する。コネクションタイプはReliable Connection、Unreliable Connection、Unreliable Datagramをサポートし、SEND、RDMA WRITE、RDMA READといったRDMAオペレーションを実装している。

最大キューペア数は1~4096まで設定可能で、PFCやVLAN/PCPタグによるフロー制御、ECNおよびCNPを用いた輻輳制御とレート制御に対応する。FPGA実装時には100Gbpsのワイヤレート転送が可能とされている。

対応デバイスは、Intel(Altera)Stratix 10およびAgilexシリーズ、AMD Alveo(UltraScale+)およびVersalシリーズで、DDRおよびHBMメモリ構成の双方に対応する。

提供スケジュール

本RoCEv2 RDMA IPは、2025年12月22日より評価および購入が可能となる。加えて、200Gbps対応版のリリースが2026年3月末に予定されている。

www.i-highway.com