www.engineering-japan.com

20

'21

Written on Modified on

IoT向けマイコンの低消費電力化に向けて、混載メモリ用STT-MRAMの書き換え技術を開発

16nm FinFETロジック混載STT-MRAMの試作チップで、データ書き換えの消費電力低減と高速化を実証、IEDM 2021にて発表。

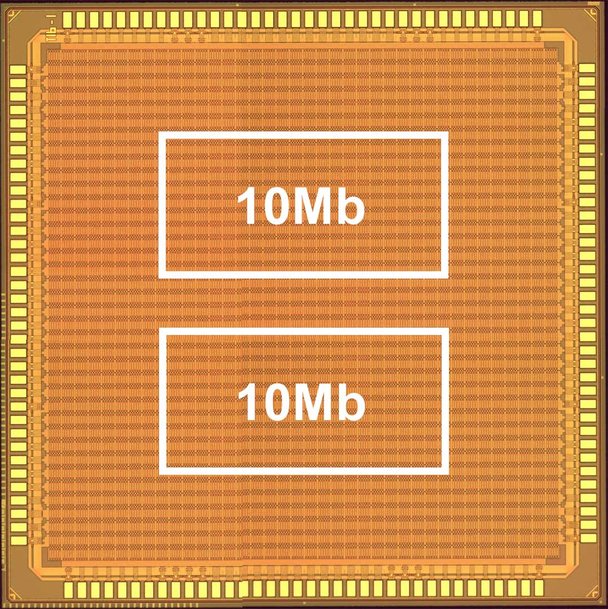

ルネサス エレクトロニクス株式会社(代表取締役社長兼CEO:柴田 英利、以下ルネサス)は、このたびスピン注入磁化反転型磁気抵抗メモリ(STT-MRAM、以下MRAM)の書き換えに必要なエネルギと電圧印加時間の低減を実現する技術を開発しました。16nm FinFETロジック混載MRAMプロセスにおいて、20Mbit(メガビット)のMRAMメモリセルアレイを搭載したテストチップを試作し、書き換えエネルギの72%低減と、電圧印加時間の50%低減を実証しました。新技術は、(1)データ書き換え動作によるメモリセル毎の状態変化を適切な時間で確実に検知して、自動的に書き換え電圧の印加を終了するスロープパルスを用いた自己終端書き込み技術と、(2)同時書き換えビット数の最適化技術です。これらにより、低消費電力かつ高速なMRAMの書き換えが可能になります。

ルネサスは本成果を、2021年12月11日から15日までサンフランシスコで開催されている「2021 国際電子デバイス会議 (2021 International Electron Device Meeting:IEDM)」で、12月13日に発表しました。

近年、IoT化の加速により、エンドポイントの機器に使用されるマイコンには、低消費電力化が強く求められています。MRAMは書き換えに必要なエネルギがフラッシュメモリより小さく、特に頻繁な書き換えを伴う用途では本質的に有利です。しかし、マイコンに一層高い処理能力が求められる中で、パフォーマンスと消費電力のトレードオフの制約を緩和するために、低消費電力化が依然大きな課題となっています。

こうした要求に応えるためにルネサスが新たに開発したMRAM書き換え技術は以下の通りです。

(1)スロープパルス方式を用いた自己終端書き換え

MRAMは、磁気トンネル結合(MTJ)素子の高抵抗状態と低抵抗状態をデータ”1”および”0”に対応させて情報を記憶します。従来、書き換えのエネルギや電圧印加時間を低減するために、メモリセルへの書き換え電圧の印加中にメモリセル電流の変化によって書き換え完了を検知して書き換え電圧印加を自動的に停止する自己終端書き換え手法が提案されていました。しかし、メモリセル特性のばらつきや書き換え終了の検知回路の検出精度などの問題で安定した書き換え完了検知ができないという課題がありました。

この課題への対応として、従来、高抵抗状態から低抵抗状態への書き換え時に一定電圧を印加していたのに対し、時間経過とともに電圧を徐々に高くしていくスロープ電圧方式を採用しました。これにより、書き換え完了を安定して検知することを可能にしました。メモリセルの特性ばらつきなどの要因でメモリセル電流が検知回路の検知レベルに到達しなかった場合でも、その後書き換え電圧が徐々に高くなっていくことでメモリセル電流が増加し、最終的に検知レベルを越えるため、書き換えの完了を検知して、書き換え電圧の印加を終了することができます。

また、逆方向の低抵抗状態から高抵抗状態への書き換え時には、メモリセル電流が大電流から小電流に変わるため書き換え電圧をスロープで高くする方式では書き換えの完了検知ができません。そのため、電流源回路を用いて書き換え電流をスロープで増加させ、書き換え電圧がある判定電圧を越えるかどうかを電圧検知回路でモニタして完了検知を行うよう工夫しています。

(2)同時書き換えビット数の最適化技術

従来、MRAMの書き換え電圧はメモリセルの書き換え特性ばらつきのワーストビットの特性から書き込み電圧を決定していました。その場合、高い書き換え電圧が必要となるため、その発生にチャージポンプ回路を用いていました。必要なチャージポンプ回路の面積を抑えるため、例えばMRAMマクロの書き換え単位を4分割等の複数に分割して書き換えが実施されますが、その場合、分割した分だけ書き換えパルスの印加時間が倍数で長くなります。

この問題に対応するため、全ビットではなく大多数のビット(書き換え特性ばらつきの90%以上)のみを書き換える想定だと書き換え電圧を大幅に下げられることに着目しました。まず、大多数のビットをマイコンチップの外部電圧(IO用電源)からの降圧により発生可能な低い書き換え電圧で同時に書き換えます。この時、前項(1)のスロープパルス方式を適用してビット毎の特性に応じて自己終端書き換えを行います。次に、残った10%以下のビットのみチャージポンプ回路で発生した高い書き換え電圧で書き換えます。この技術により、書き換え電圧の印加は2回で完了するため、書き換え単位を4分割以上していた場合に対して50%以上書き換え電圧印加時間の高速化が可能です。また、本技術では大多数のビットは大きな電力を消費するチャージポンプではなく、外部電源からの降圧で得た電圧で書き換えを行います。そのため、書き換えエネルギの削減にも有効です。

以上の新技術を組み合わせることにより、16nm FinFETロジックプロセスへの混載MRAM技術によって試作した20MbitのMRAMメモリセルアレイを搭載したテストチップを用いた測定により、72%の書き換えエネルギの低減と50%の書き換えパルス印加時間の低減を確認しました。

ルネサスは、マイコン製品に対する混載MRAM適用に向けた要素技術開発を推進しています。今後も、新しいアプリケーションに対応してさらなる大容量、高速、低消費電力化に向けて取り組んでまいります。

www.renesas.com