www.engineering-japan.com

20

'26

Written on Modified on

ルネサス、SDV向け車載マルチドメインSoC技術を開発

チップレット対応と3nm NPU設計により、ASIL D機能安全と高効率電力制御を両立。

www.renesas.com

自動運転やデジタルコクピットを支える車載マルチドメインECUおよび車載SoC分野において、ルネサス エレクトロニクス株式会社は、SDV(Software-Defined Vehicle)時代に求められる高性能・高信頼性アーキテクチャを実現する3つの基盤技術を開発しました。本技術は、2026年2月15日から19日まで米国サンフランシスコで開催された「ISSCC 2026(International Solid-State Circuits Conference 2026)」にて発表されました。

SDV時代に求められるSoC要件

次世代の車載E/Eアーキテクチャでは、複数アプリケーションの同時実行、高いAI処理性能、柔軟な拡張性、そしてASIL Dレベルの機能安全への対応が求められます。

セントラルコンピューティング化によりSoCの大規模化が進む中、性能向上と同時に車載品質および電力効率を維持する設計が重要課題となっています。

ASIL D対応チップレットアーキテクチャ

新技術では、標準ダイ間通信規格UCIeに独自のRegionIDメカニズムを組み合わせることで、チップレット構成でもASIL Dをサポート可能なアーキテクチャを実現しました。

従来のUCIeにはRegionIDの伝送機能がないため、物理アドレス空間にRegionIDをマッピングし、UCIe領域にエンコードして送信する方式を開発。これにより、MMUやリアルタイムコアにおける安全なアクセス制御を確立し、Freedom from Interference(FFI)を実現します。

UCIe評価では51.2GB/sの高速通信を達成し、SoC内部バスの上限に迫る帯域を確認しました。これにより、拡張性と機能安全を両立した高性能車載SoC設計が可能となります。

3nmプロセスによる大規模NPUと車載品質

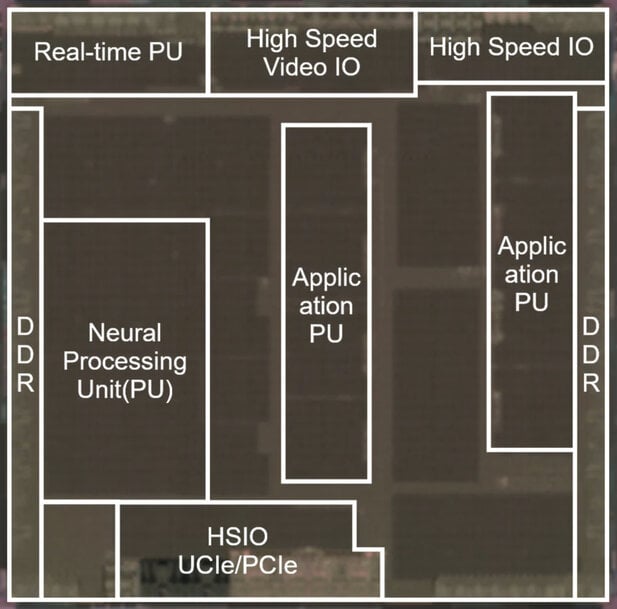

AI処理性能向上のため、3nmプロセスを採用したSoCにおいてNPU(Neural Processing Unit)を大規模化。NPU面積は前世代比で約1.5倍に拡大しています。

大規模化に伴うクロックレイテンシ増大への対策として、従来のモジュール単位CPGを分割し、サブモジュール階層にmini-CPG(mCPG)を配置。これによりクロック遅延を大幅に低減し、タイミング要件を満たしました。

さらに、テストモード時も上位・下位mCPGを同一クロック源で同期させる設計を採用。ユーザークロックとテストクロックを単一経路化することで、大規模SoCでもゼロディフェクト水準の品質確保を可能にしています。

90超の電源ドメインによる高効率電力制御

高性能化に伴う消費電力増加に対応するため、90以上の電源ドメインを用いた高度なパワーゲーティング技術を開発しました。数mWから数十Wまでの精密制御が可能です。

IRドロップ低減のため、パワースイッチをリング型と行配置型に分割。電源投入時はリング型でラッシュ電流を抑制し、その後行型でインピーダンスを均一化することで、従来比約13%のIRドロップ改善を達成しました。

機能安全面では、DCLS(Dual Core Lock Step)構成においてマスターとチェッカーを独立制御。さらにデジタル電圧モニタ(DVMON)を採用し、エージング耐性を1.4mV向上させています。

R-Car X5Hへの適用

これらの技術は、車載マルチドメインECU用SoC「R-Car X5H」に採用されています。同SoCは、自動運転やデジタルコクピットなど複数アプリケーションを同時に実行しながら機能安全を確保し、SDVの実現を加速するプラットフォームとなります。

今回発表された技術は、高性能AI処理、チップレット拡張性、そして車載品質を統合する設計手法として、今後の車載SoC開発の基盤技術となるものです。

www.renesas.com